# R6500/1E Microprocessor Emulator Device

### INTRODUCTION

The R6500/1E device provides all the features of the R6500/1 Microcomputer in a ROMless form suitable for use as an advanced microprocessor complete with 16-bit counter and 32 I/O lines, and an address and data bus for 4K of external memory.

To aid in designing R6500/1 microcomputer systems, it may also be used as an emulator device. Device architecture is basically the same as the R6500/1 except that the address, data, and associated control lines are routed off the chip for connection to an external memory.

The functions and operation of the R6500/1E device are identical to the R6500/1 except for minor differences noted in this document. The R6500/1 Product Description (Order No. 212) contains a description of R6500/1 functions and interface signals.

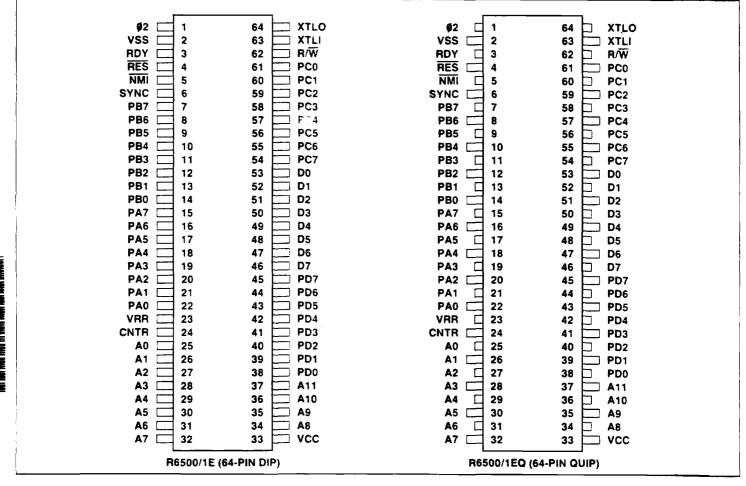

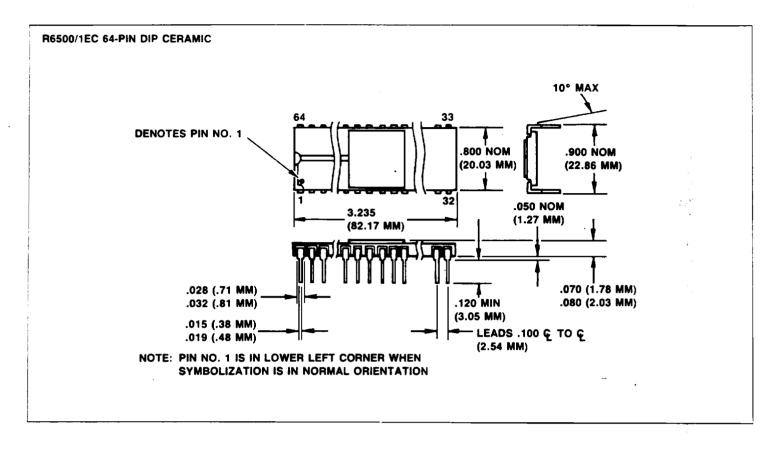

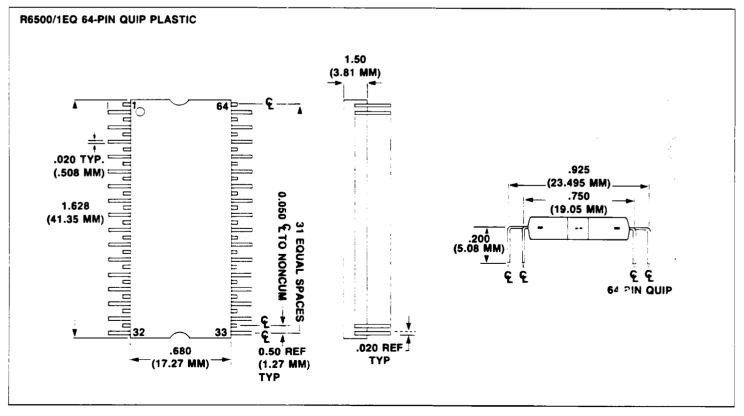

The R6500/1E device is available in both 64-pin ceramic DIP (R6500/1EC) and 64-pin plastic QUIP (R6500/1EQ).

### **ORDERING INFORMATION**

| Part<br>Number | Package<br>Type | Frequency<br>Option | Temperature<br>Range |

|----------------|-----------------|---------------------|----------------------|

| R6500/1EC      | Ceramic         | 1 MHz               | 0°C to 70°C          |

| R6500/1EAC     | Ceramic         | 2 MHz               | 0°C to 70°C          |

| R6500/1EQ      | Plastic         | 1 MHz               | 0°C to 70°C          |

| R6500/1EAQ     | Plastic         | 2 MHz               | 0°C to 70°C          |

R6500/1E Pin Assignments

### R6500/1E

## Microprocessor Emulator Device

### INTERFACE SIGNALS

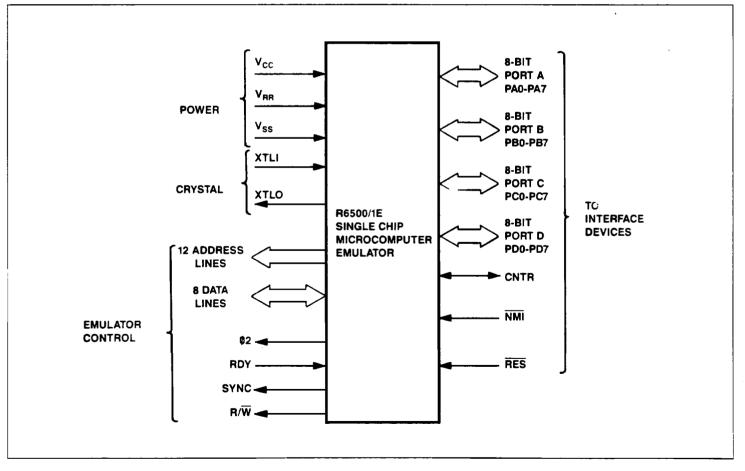

All R6500/1 interface signals are available in the R6500/1E microcomputer plus the additional address (12), data (8), and control (4) lines required to extend the address bus and the data bus external to the device. The R6500/1E emulator unique interface signals are shown in Figure 1 and are described in Table 1. While the pin assignments are different in order to accommodate 64-pin DIP and QUIP packages, the interface characteristics of signals common to the R6500/1 are identical.

### SYSTEM ARCHITECTURE

The architecture of the R6500/1E is identical to the R6500/1 with the following differences:

#### EXTERNAL ADDRESSING

ROM addressing is routed externally in the R6500/1E. The address range for internal ROM in the R6500/1 (\$800-\$FF9) is available externally for connection to ROM or RAM devices(s).

An additional 1024 bytes (\$400-\$7FF) are decoded for external memory access. Note that this address range can be used for

debugging with the R6500/1E but cannot be used when the object code is transferred to masked ROM in an R6500/1 (which is restricted to \$800-\$FF9).

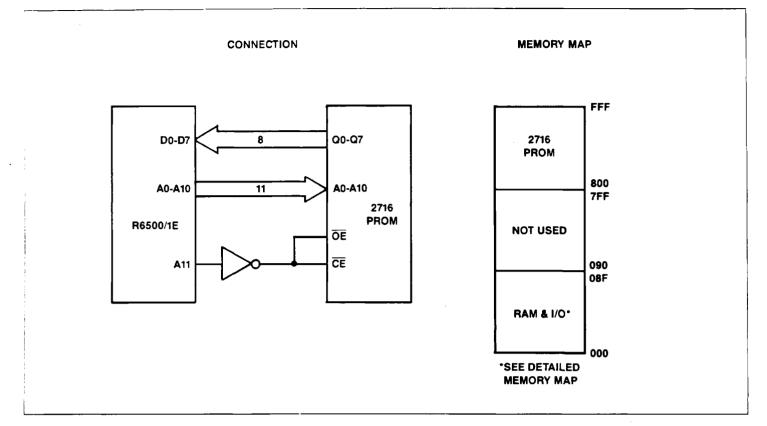

A memory map of the R6500/1E is shown in Figure 2.

#### INTERNAL I/O PORT PULL-UPS

The R6500/1E has the internal I/O and CNTR port pull-up resistors only. The option to delete the pull-up resistors is not available for the R6500/1E.

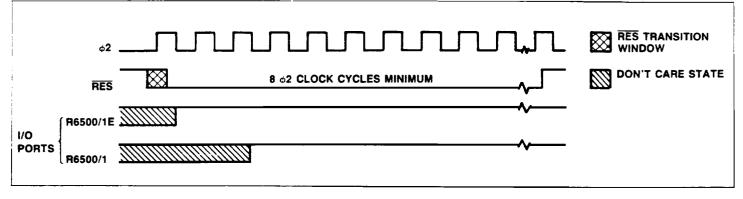

#### EARLIER I/O PORT INITIALIZATION

Ports A, B, C, D and the CNTR line in the R6500/1E are initialized to the logic high state two  $\emptyset$ 2 clock cycles earlier than in the R6500/1. It is still required, however, that the RES line be held low for at least eight  $\emptyset$ 2 clock cycles after VCC reaches operating range (Figure 3).

#### WRITE-ONLY MONITORING

The R6500/1E allows the user to monitor write operations to the internal RAM and I/O by routing those operations externally as well as internally. Read operations are not routed externally.

Figure 1. R6500/1E Emulator Interface Diagram

•~

#### Table 1. R6500/1E Emulator Unique Signals Description

| Signal<br>Name | Pin<br>No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/W            | 62         | Read/Write. Read/Write allows the CPU to control the direction of data transfer between the R6500/1E Emulator CPU and external memory. This line is high when reading data from memory and is low when writing data to memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RDY            | 3          | <b>Ready.</b> The Ready input delays execution of any cycle during which the RDY line is low. This allows the user to halt or single step the CPU on all cycles except write cycles. A negative transition to the low state during the \$2 clock low pulse will halt the CPU with the address lines containing the current address being fetched. If RDY is low during a write cycle, it is ignored until the following read operation. This condition will remain through a subsequent \$2 clock pulse in which the RDY line is low. This feature allows the CPU to interface with memories having slow access times, such as EPROMS used with the R6500/1E during prototype system development. |

| SYNC           | 6          | Sync. The Sync signal is provided to identify cycles in which the CPU is performing OP CODE fetch. SYNC goes high during the Ø2 clock low pulse of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the Ø2 clock low pulse in which SYNC went high, the CPU will halt in its current state and will remain in that state until the RDY line goes high. Using this technique, the SYNC signal can be used to control RDY to cause single instruction execution.                                                                                                                                                                               |

| Ø2             | 1          | Phase 2 (02) clock: Data transfer takes place only during 02 clock pulse high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A0-A11         | 25-37      | Address Bus Lines. The address bus buffers on the R6500/1E are push/pull type drivers capable of driging at least 130 pF and one standard TTL load. The address bus always contains known data. The addressing tgechnique involves putting an address on the address bus which is known to be either in program sequence, on the same page in program memory, or at a known point in memory. The I/O address commands are also placed on these lines.                                                                                                                                                                                                                                             |

| D0-D7          | 53-46      | Data Bus Lines. All transfers of instructions and data between the CPU and memory, I/O, and other interfacing circuitry take place on the bidirectional data bus lines. The buffers driving the data bus lines have full three-state capability. Each data bus pin is connected to an input and output buffer, with the output buffer remaining in the floating condition.                                                                                                                                                                                                                                                                                                                        |

| IRQ VECTOR HIGH<br>IRQ VECTOR LOW<br>RES VECTOR LOW<br>RES VECTOR LOW<br>NMI VECTOR HIGH<br>NMI VECTOR LOW<br>R6500/1 USER PROGRAM<br>R6500/1 USER PROGRAM AREA (1)<br>UNASSIGNED<br>CONTROL REGISTER<br>UNASSIGNED<br>CLEAR PA1 NEG EDGE DETECTED<br>CLEAR PA1 NEG EDGE DETECTED<br>CLEAR PA0 POS EDGE DETECTED<br>(2<br>UPPER LATCH AND TRANSFER LATCH TO COUNTER (3<br>LOWER COUNT<br>LOWER LATCH | 089 only at 000-03F. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| LOWER LATCH UPPER LATCH PORT D PORT C PORT B PORT A UNASSIGNED USER RAM                                                                                                                                                                                                                                                                                                                              | 085                  |

Figure 2. R6500/1E Memory Map

Figure 3. R6500/1E I/O Port Initialization

4

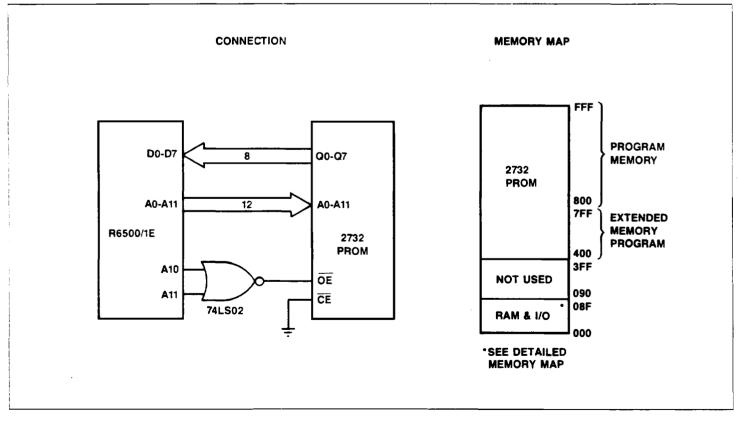

### TYPICAL PROGRAM MEMORY INTERCONNECTIONS

Two typical connections between the R6500/1E and program memory (in this case, type 2716 and 2732 PROMS) are illustrated. Figure 4 shows a connection to a 2K 2716 PROM. Since the R6500/1 has a 2K ROM capacity, the contents of the PROM could be masked directly into the production R6500/1 ROM.

Figure 5 shows a connection to a 4K 2732 PROM. Only 3K bytes (\$400-\$FFF) are enabled. The upper 2K bytes correspond the production ROM space (\$800-\$FFF) in the R6500/1. The extra 1K (\$400-\$7FF) allows expanded or additional programs to be used during R6500/1 firmware development. The production program, however, must be reduced to 2K maximum (\$800-\$FFF) before masking into R6500/1 ROM.

### R6500/1E

Figure 4. R6500/1E Connected to One 2716 PROM (2K Bytes)

Figure 5. R6500/1E Connected to One 2732 PROM (3K Bytes)

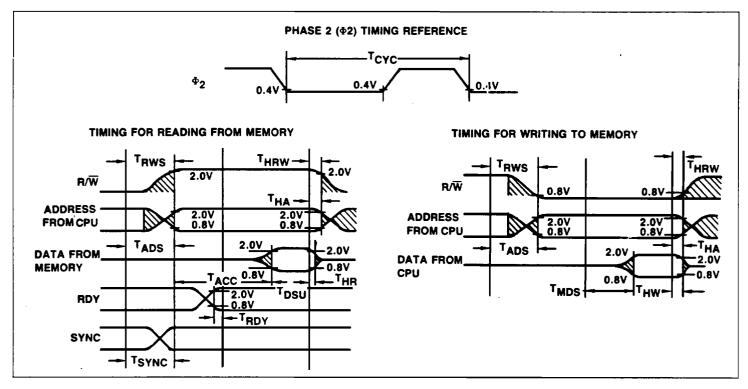

### **DEVICE TIMING**

|                             |                 | 1 MHz |      | 2 MHz |             |      |

|-----------------------------|-----------------|-------|------|-------|-------------|------|

| Signal                      | Symbol          | Min.  | Max. | Min.  | Max.        | Unit |

| R/W setup time from CPU     | TRWS            |       | 300  |       | 200         | ns   |

| Address setup time from CPU | TADS            |       | 300  | •     | <b>20</b> 0 | ns   |

| Memory read access time     | TACC            |       | 525  |       | <b>2</b> 25 | ns   |

| Data stabilization time     | TDSU            | 150   |      | 75    |             | ns   |

| Data hold time Read         | T <sub>HR</sub> | 10    |      | 10    |             | ns   |

| Data hold time — Write      | THW             | 30    |      | 30    |             | ns   |

| Data delay time from CPU    | TMDS            |       | 200  |       | 150         | ns   |

| RDY setup time              | TRDY            | 100   |      | 50    |             | ns   |

| SYNC delay time from CPU    | TSYNC           |       | 350  |       | 175         | ns   |

| Address hold time           | THA             | 30    |      | 30    |             | ns   |

| R/W hold time               | THRW            | 30    |      | 30    |             | ns   |

| Cycle Time                  | TCYC            | 1.0   | 10.0 | 0.5   | 10.0        | μs   |

### **TIMING DIAGRAMS**

### **MAXIMUM RATINGS\***

| Parameter             | Symbol           | Value         | Unit |

|-----------------------|------------------|---------------|------|

| Supply Voltage        | V <sub>cc</sub>  | -0.3 to +7.0  | Vdc  |

| Input Voltage         | V <sub>IN</sub>  | -0.3 to +7.0  | Vdc  |

| Operating Temperature | TA               | 0 tc + 70     | °C   |

| Storage Temperature   | T <sub>STG</sub> | - 55 to + 150 | °C   |

\*NOTE: Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device atr these or any other conditions above those indicated in other sections of this document is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### ELECTRICAL CHARACTERISTICS

(V\_{CC} = 5.0  $\pm$  5%, V\_{SS} = 0, T\_A = 0°C to 70°C unless otherwise specified)

| Characteristic                                                        | Symbol                              | Min         | Тур | Max             | Unit | Test Conditions                                      |  |

|-----------------------------------------------------------------------|-------------------------------------|-------------|-----|-----------------|------|------------------------------------------------------|--|

| RAM Standby Voltage (Retention Mode)                                  | V <sub>RR</sub>                     | <b>3</b> .5 | _   | V <sub>cc</sub> | v    |                                                      |  |

| RAM Standby Current (Retention Mode)                                  | I <sub>RR</sub>                     | —           | 10  |                 | mA   |                                                      |  |

| Input High Voltage                                                    | V <sub>iH</sub>                     | + 2.4       |     |                 | Vdc  |                                                      |  |

| Input Low Voltage                                                     | V <sub>IL</sub>                     | _           |     | + 0.8           | Vdc  |                                                      |  |

| Three-State (Off State) Input Current<br>D0-D7                        | I <sub>TSI</sub>                    | _           |     | ± 10            | μΑ   | $V_{IN} = 0.4 \text{ to } 2.4V$<br>$V_{CC} = 5.25V$  |  |

| Output High Voltage<br>D0-D7, SYNC, A0-A11, R/W, Ø2                   | V <sub>OH</sub>                     | + 2.4       |     |                 | Vdc  | $I_{LOAD} = -100 \ \mu A$<br>V <sub>CC</sub> = 4.75V |  |

| Output Low Voltage<br>D0-D7, SYNC, A0-A11, R/W, Ø2                    | V <sub>OL</sub>                     | _           | _   | + 0.6           | Vdc  | $I_{LOAD} = 1.6 \ \mu A$ $V_{CC} = 4.75 V$           |  |

| Power Dissipation ( $V_{CC} = 5.5V$ )                                 | PD                                  | -           | 750 | 1200            | μW   | $V_{CC} = 5.5V$                                      |  |

| Input Capacitance<br>RDY, PA, PB, PC, PD, CNTR<br>D0-D7<br>XTLI, XTLO | C <sub>IN</sub>                     | -           |     | 10-<br>15<br>50 | ρF   | $T_A = 25^{\circ}C$<br>$V_{IN} = 0$                  |  |

| Output Capacitance<br>A0-A11, R/W, SYNC<br>Ø2                         | C <sub>OUT</sub><br>C <sub>¢2</sub> |             |     | 12<br>80        | pF   | f = 1 MHz                                            |  |

| I/O Port Pull-up Resistance                                           | R                                   | 3.0         | 6.0 | 11.5            | kohm |                                                      |  |

1. Typical values measured at  $T_A = 25^{\circ}C$  and  $V_{CC} = 5.0V$ .

2. Negative sign indicates outward current flow, positive indicates inward flow.

#### PACKAGE DIMENSIONS

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any intringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document subject to change without notice.

#### Headquarters

Digital Communications Division Rociovell International 4311 Jamboree Road P.O. Box C Newport Beach, CA 92658-8902 Tel: (714) 833-4600 Fax: (714) 833-4078 Fax: (714) 833-4391

#### USA - Southwest

Digital Communications Division Rociovell International 5000 Birch Street Suite 400 Newport Beach, CA 92660 Tel: (714) 833-4655 Fax: (714) 833-6898

USA - Southeast Digital Communications Division **Bociovell International** One Copley Parkway Suite 210 Morrisville, NC 27560 Tel: (919) 467-7703 Fax: (919) 467-6096

USA - South Central Digital Communications Division Rockwell International 2001 N. Collins Blvd. Suite 103 Richardson, TX 75080 Tel: (214) 994-4020 Fax: (214) 994-4028

USA - North Central Digital Communications Division Rockwell International 3158 South River Road Suite 204 Des Plaines, IL 60018 Tel: (708) 297-8875 Fax: (708) 297-3230

#### **DIGITAL COMMUNICATIONS DIVISION REGIONAL SALES OFFICES**

USA - Mid Atlantic Digital Communications Division Rockwell International 5001-B Greentree Executive Campus Route 73 Marton, NJ 08053 Tel: (609) 596-0090 Fax: (609) 596-5681

USA - Northeast (and Canada East) Digital Communications Division Rockwell international 239 Littleton Road Suite 1B Westford, MA 01886 Tel: (508) 692-7660 Fax: (508) 692-8185

USA - Northwest (and Canada West) Digital Communications Division Rockwell International 3600 Pruneridge Avenue Suite 10C Santa Clara, CA 95051 Tel: (408) 249-9696 Fax: (408) 249-6518

Australia

Digital Communications Division Rockweil International 3 Thomas Holt Drive P.O. Box 165 North Ryde, NSW 2113 Australia Tel: (61-2) 805-5555 Fax: (61-2) 805-5599

#### France

Digital Communications Division Rockwell International Tour GAN, 16 Place de l'Iris Cedex 13 92082 Paris La Delense 2 France Tel: (33-1) 49-06-39-80 Fax: (33-1) 49-06-39-90

#### Germany

Digital Communications Division Rockwell International GmpH Paul-Gerhardt-Allee 50 a 8000 München 60 Germany Tel: (49-89) 829-1320 Fax: (49-89) 834-2734

Hong Kong Digital Communications Division Rockwell International 13th Floor Suites 6-10, Harbour Centre 25 Harbour Road Wanchai, Hong Kong Tel: (852) 827-0181 Fax: (852) 827-6488

Italy

Digital Communications Division Rockwell International Corporation Via Tortona, 33 20144 Milano lia iy Tel: (39-2) 47790-226

Fax: (39-2) 4120-642

Japan

Digital Communications Division Rockwell International Japan Co., Ltd Sogo Hanzomon Building, BF 1-7 Kojimachi, Chiyoda-ku Tokyo, 102 Japan Tel: (81-3) 3265-8808 Fax: (81-3) 3263-0639

#### Korea

Digital Communications Division **Rockwell International** Rm. 608 Leema Building 146-1 Soosong-Dong Chongro-Ku Seoul Korea Tel: (82-2) 736-9121 Fax: (82-2) 736-9124

#### Taiwan **Digital Communications Division**

Rockwell International Room 2808 International Trade Building 333 Keelung Road, Section 1 Taipei, Taiwan 10548 R.O.C. Tel: (886-2) 720-0282 Fax: (886-2) 757-6760

#### **United Kingdom**

Digital Communications Division Rockwell International Ltd. Central House 3, Lampton Road Hounslow, Middlesex TW3 1HY England Tel: (44-81) 577-1034 Fax: (44-81) 570-0758